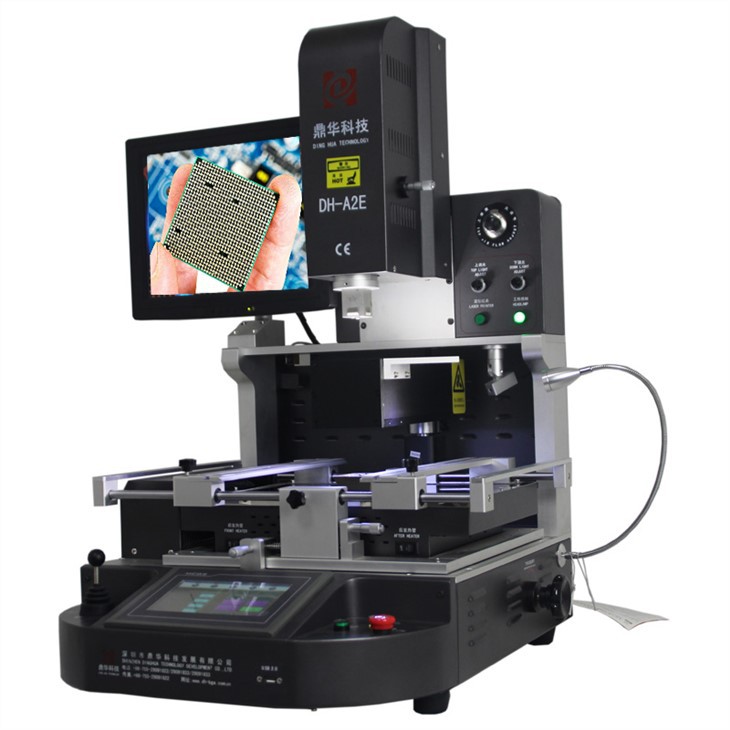

Auto Optical BGA Rework Station

Široko se koristi u popravku na razini čipa za matičnu ploču mobilnog telefona, prijenosnog računala, računala, TV-a, klima uređaja itd. Ima visoku stopu uspješnosti popravka i visok stupanj automatizacije te štedi puno ljudskih napora. Mi smo profesionalni proizvođač ovog stroja i imamo ove strojeve dostupne na zalihama.

Opis

Auto Optical BGA Rework Station

1. Primjena Auto Optical BGA Rework Station

Matična ploča računala, pametnog telefona, laptopa, MacBook logičke ploče, digitalne kamere, klima uređaja, TV-a i druge elektroničke opreme

oprema iz medicinske industrije, industrije komunikacija, automobilske industrije itd.

Prikladno za različite vrste čipova: BGA, PGA, POP, BQFP, QFN, SOT223, PLCC, TQFP, TDFN, TSOP, PBGA, CPGA, LED čip.

2. Značajke proizvoda Auto Optical BGA Rework Station

• Visoka stopa uspješnosti popravka na razini krhotina. Proces odlemljivanja, montaže i lemljenja je automatski.

• Precizno poravnanje svakog lemnog spoja može se zajamčiti pomoću CCD kamere za optičko poravnanje.

•Precizna kontrola temperature može se osigurati s 3 neovisna područja grijanja. Stroj može postaviti i spremiti

1 milijun temperaturnog profila.

• Ugrađeni vakuum u montažnoj glavi automatski preuzima BGA čip nakon dovršetka odlemljivanja.

3.Specifikacija automatske optičke BGA stanice za preradu

4. Pojedinosti o Auto Optical BGA Rework Station

CCD kamera (sustav preciznog optičkog usmjeravanja) ; 2.HD digitalni zaslon; 3. Mikrometar (podešavanje kuta strugotine) ;

4.3 neovisni grijači (vrući zrak i infracrveni); 5. Lasersko pozicioniranje ; 6. HD sučelje zaslona osjetljivog na dodir, PLC kontrola;

7.Led prednje svjetlo ; 8. Upravljanje džojstikom.

5. Zašto odabrati našu automatsku optičku BGA stanicu za preradu?

6. Certifikat Auto Optical BGA Rework Station

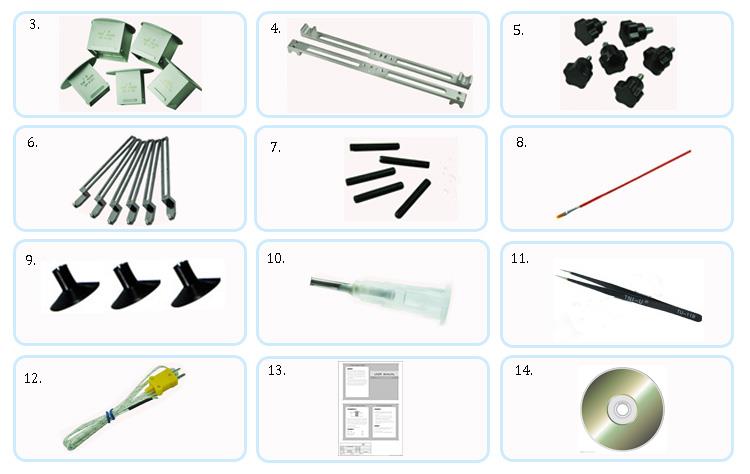

7. Pakiranje i otprema automatske optičke BGA stanice za preradu

8.FAQ

Kako testirati čip?

Početni test čipa na razini sustava

SoC se temelji na dubokim submikronskim procesima, tako da testiranje novih Soc uređaja zahtijeva potpuno novi pristup. Budući da svaka funkcionalna komponenta

ima svoje vlastite zahtjeve za testiranje, projektant mora napraviti plan testiranja rano u procesu projektiranja.

Plan testiranja blok po blok za SoC uređaje mora biti implementiran: ispravno konfigurirani ATPG alati za logičko testiranje; kratko vrijeme ispitivanja; novi brzi

modeli grešaka i višestruki testovi memorije ili malih polja. Za proizvodnu liniju, dijagnostička metoda ne samo da pronalazi grešku, već i odvaja

neispravan čvor od radnog čvora. Nadalje, treba koristiti tehnike multipleksiranja testova kad god je to moguće kako bi se uštedjelo vrijeme testiranja. Na području visoko

integrirano IC testiranje, ATPG i IDDQ-ove tehnike projektiranja koje se mogu testirati imaju snažan mehanizam za odvajanje grešaka.

Ostali stvarni parametri koje je potrebno planirati unaprijed uključuju broj pinova koje je potrebno skenirati i količinu memorije na kraju svakog pina.

Granična skeniranja mogu se ugraditi u SoC, ali nisu ograničena na testove međusobnog povezivanja na pločama ili modulima s više čipova.

Iako se veličina čipa smanjuje, čip još uvijek može sadržavati milijune do 100 milijuna tranzistora, a broj načina testiranja porastao je do dosad neviđenih

razine, što rezultira duljim ciklusima ispitivanja. Ovaj problem se može testirati. Način kompresije za rješavanje, omjer kompresije može doseći 20 posto do 60 posto. Za današnje velike razmjere

dizajn čipa, kako bi se izbjegli problemi s kapacitetom, potrebno je pronaći testni softver koji može raditi na 64-bitnim operativnim sustavima.

Osim toga, testni softver se suočava s novim problemima testiranja uzrokovanim dubokim submikronskim procesima i sve većom učestalošću. U prošlosti, ATPG način testiranja za

testiranje grešaka statičkog blokiranja više nije bilo primjenjivo. Dodavanje funkcionalnih uzoraka tradicionalnim alatima otežalo je pronalaženje novih grešaka. Bolji pristup je da se

klasificirati skupine prošlih funkcionalnih načina rada kako bi se utvrdilo koji se kvarovi ne mogu otkriti, a zatim izraditi ATPG način rada za hvatanje tih tipova kvarova koji nedostaju.

Kako se projektirani kapacitet povećava, a vrijeme ispitivanja po tranzistoru smanjuje, kako bi se pronašli problemi povezani s brzinom i provjerilo vremensko usklađivanje kruga, sinkrona metoda ispitivanja

mora biti zaposlen. Sinkrono testiranje mora uključivati višestruke modele grešaka, uključujući prijelazne modele, kašnjenja puta i IDDQ.

Neke tvrtke u industriji vjeruju da bi kombiniranje blokirajućih, funkcionalnih i prijelaznih/kašnjenja puta moglo biti najučinkovitija strategija testiranja. Za duboko

submikronski čipovi i visokofrekventni rad, ispitivanje prolaznih pojava i kašnjenja puta još je važnije.

Kako bi se riješio problem ATE točnosti pri sinkronizaciji testne jezgre i smanjili troškovi, potrebno je pronaći novu metodu koja pojednostavljuje sučelje

testni uređaj (prijelazni test i test kašnjenja putanje zahtijeva točan sat na sučelju ispitnog uređaja), osigurava da je signal dovoljno točan tijekom testa.

Budući da postoji velika mogućnost proizvodnih grešaka u memorijskom bloku SoC-a, memorijski BIST mora imati dijagnostičku funkciju. Nakon što se pronađe problem,

neispravna adresna jedinica može se mapirati u redundantnu memoriju rezervne adresne jedinice, a otkrivena adresa greške će biti odbačena. Izbjegavajte odbacivanje

cijeli skupi čip.

Testiranje malih ugrađenih memorijskih blokova eliminira potrebu za dodatnim vratima ili kontrolnom logikom. Na primjer, tehnike testiranja vektorske pretvorbe mogu pretvoriti

funkcionalne načine rada u niz načina skeniranja.

Za razliku od BIST metode, funkcionalni ulaz premosnog memorijskog bloka ne zahtijeva dodatnu logiku. Budući da nije potrebna dodatna testna logika, SoC

razvojni inženjeri mogu ponovno koristiti testne obrasce koji su formirani u prošlosti.

Napredni ATPG alati ne samo da paralelno testiraju makronaredbe, već i utvrđuju postoje li sukobi, kao i detalje koji se makronaredbe mogu testirati paralelno, a koji

makronaredbe se ne mogu testirati paralelno. Osim toga, ove se makronaredbe mogu učinkovito testirati čak i ako je takt makronaredbe isti kao sat skeniranja (kao što je sinkrona memorija).

Trenutačno nema dovoljno ispitnih točaka na gustoj dvostranoj ploči, a svaki složeni čip mora biti opremljen krugom graničnog skeniranja. Bez

granična skeniranja, traženje grešaka u proizvodnji na razini ploče prilično je teško i ne može se ni pronaći. Uz granično skeniranje, testiranje na razini ploče iznimno je jednostavno

i neovisno o logičkom sklopu unutar čipa. Granično skeniranje također može konfigurirati ATPG način rada za lanac skeniranja čipa u bilo kojoj fazi proizvodnje.